A few weeks ago, the big news was that the research alliance of IBM, Global Foundries and Samsung unveiled the world’s first 5 nm chip as we could all read everywhere over the internet [1]. Most notable was however the fact that they reported the use of horizontal gate-all-around field-effect-transistors (GAA-FETs) in which they actually used three nanosheets stacked on top of each other as channel between source and drain. I think that this aspect, and the fact that they showed a very cool transmission-electron-microscopy (TEM) image (see below), probably contributed a lot to the vast amount of attention that the announcement received. These aspects might have been more important than the fact that really a 5 nm technology device was revealed. From the information provided, I even wouldn’t be able to tell if it would qualify as 5 nm as there was no scale-bar in the TEM image and I couldn’t find any other supporting evidence e.g., in terms of performance. Yet, it clearly showed some important progress made in terms of semiconductor scaling. By the way, a year ago, imec already reported similar GAA-FETs with nanowires at the 2016 Symposia on VLSI Technology & Circuits (Honolulu HI, June 13-17, 2016) [2] as you can see in the other TEM image below (now with scale bars). Well, this blog post is not really meant to discuss the devices nor the technology node they belong too. Yet, the GAA-FETs are a nice way to underline the rapidly growing importance of atomic scale processing (ASP) and that is exactly what I want to do here.

TEM image of IBM Research Alliance’s 5nm transistor consisting of a stack of silicon nanosheets with gate-all-around. [1]

TEM images of imec’s gate-all-around FETs with silicon nanowires of 8 nm in diameter. [2] [3]

As reported in the announcement, the fabrication of the GAA-FETs wouldn’t have been possible without the technique of atomic layer deposition (ALD). This is not really news as ALD has become important since the 45 nm node and became really essential when switching from 2D FETs to 3D finFETs. However, to deposit a high-k metal gate stack all around the nanowires – or nanosheets – is even more challenging than covering a silicon fin. So it can safely be stated that ALD has become even more important now.

Another method that is important in the fabrication of these GAA-FETs is an isotropic etch process, which is claimed to be “atomic layer etching” (ALEt) in a nice article in Ars Technica [4] about the announcement by the IBM Research Alliance. Such an isostropic etch step is necessary after forming fins from the Si and SiGe stacks (see figure below). At some point the SiGe needs to be removed very carefully between the Si leaving behind the Si nanosheets (which are strained due to the SiGe that was present in the first place) with gaps in between. Obviously, the ALD discussed above comes in only after this etching.

The question is which process has been used for etching the SiGe and whether it really qualifies as ALEt. In the article by Ars Technica it was speculated that the etching was probably done by an Applied Materials Selectra machine [5]. However I could also imagine that it was done by a wet chemical etch step. In any case, what is most important here is that one will prefer dry etch processes in the future (see e.g., the process reported by Bernola et al. [6]) and preferably these processes really qualify as ALEt. The latter would guarantee that the etch step can be controlled at the atomic scale and therefore isvery precise. Note that the ALEt process necessary in this part of GAA-FET fabrication should be isotropic and not anisotropic as is the case for most ALEt processes reported to date [7]. The anisotropy is typically obtained by the directional ion bombardment (i.e., the ions come in perpendicular to the wafer surface) that is exploited in plasma etching. However, in this GAA-FET case, a more chemical etch is preferred such that the SiGe is also etched from the side of the fins [7].

TEM images showing the stages of building the 5 nm GAA-FET from the IBM Research Alliance. [1]

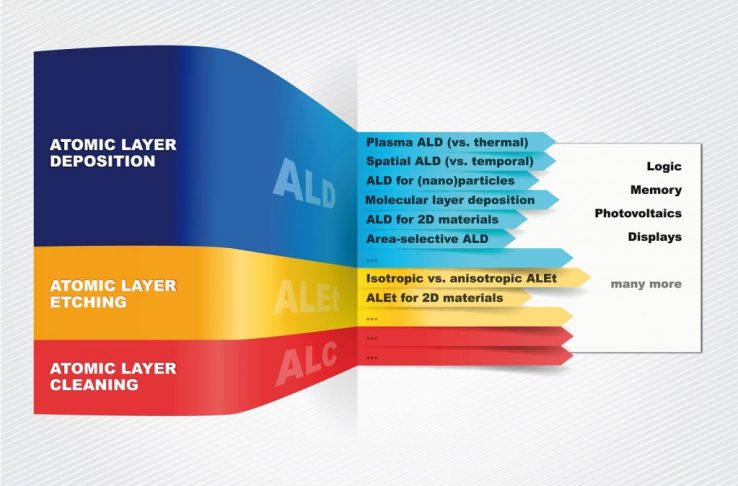

The results in the IBM Research Alliance announcement mentioned above are just one typical case and many other examples exist that reveal that atomic-scale processing is growing vastly in importance. Just think about the developments in 3D NAND in memory [8], encapsulation in flexible OLED displays [9] or the use of nanolayers in photovoltaic cells [10]. To point out this growing importance, I have made the figure below. This figure focuses on the atomic layer techniques that qualify as atomic-scale processes: atomic layer deposition (ALD), atomic layer etching (ALEt) and atomic layer cleaning (ALC). From these techniques, ALD is already established and currently a lot of work is being done to make ALEt to get there as well. The situation about ALC is not so clear although some people have already coined the name. Even a special issue of ECS Journal of Solid State Science and Technology has appeared with the title Focus Issue on Atomic Layer Etching and Cleaning [11].

The figure also displays a few typical applications for which the methods are or can be used. ALD is used in production for all those applications specifically mentioned and the expectation is that this list will grow rapidly. Eventually also ALEt and ALC will probably penetrate the production lines of many of these applications.

In the figure, I have also tried to list the most important research trends with respect to the atomic scale processing methods. Obviously the list is quite subjective but I think it covers quite well what is trendy. The trends in the field of ALD are pretty clear but for ALEt I have only been able to list two trends so far. I’m sure there are quite a few more and I would certainly appreciate your feedback on that. Just leave a comment below. Comments on the figure itself are also very welcome as I’m sure it can be updated and improved (I will certainly do this). The figure is far from comprehensive although I must admit that having a comprehensive (and rather complex) figure is not what I’m aiming for. I just want to point out what is going on in the field of atomic scale processing and convey the message that this is just the start: we are at the dawn of atomic-scale processing.

With atomic-scale processing becoming very important in many applications, techniques and methods are presently being developed and refined to allow for this processing at the atomic scale. This figure shows several atomic layer techniques which receive currently a lot of attention but several other processing techniques (e.g., CVD of 2D materials) qualify as well. The figure also indicates some research fields that are currently very trendy. Advancement in these research fields will be necessary to expand the capabilities and “toolbox” for atomic-scale processing. As described in the text, please feel free to comment on this figure and give suggestions for improvements and/or extensions.

References

[1] IBM News Room – “IBM Research Alliance Builds New Transistor for 5nm Technology”

[2] imec press release – “Imec Demonstrates Gate-All-Around MOSFETs with Lateral Silicon Nanowires at Scaled Dimensions”

[3] phys.org – “Imec demonstrates gate-all-around MOSFETs with lateral silicon nanowires at scaled dimensions”

[4] Ars Technica – “IBM unveils world’s first 5nm chip”

[5] Applied Materials Selectra

[6] Dry etch challenges in Gate All Around Devices for sub 32 nm applications, S. Bernola et al., ECS Transactions 16, 923 (2008).

[7] Atomic Layer Etching: What Can We Learn from Atomic Layer Deposition?, T. Faraz, H.C.M. Knoops, F. Roozeboom, W.M.M. Kessels, ECS J. Solid State Sci. Technol. 4, N5023 (2015).

[8] See e.g., EE Times – “First look at Samsung’s 48L 3D V-NAND Flash”

[9] See e.g., Seeking Alpha – “Samsung And LG Move To ALD For Flexible OLEDs, Could Push Applied Materials Out Of The Market”

[10] See e.g., Status and prospects of Al2O3-based surface passivation schemes for silicon solar cells, G. Dingemans and W.M.M. Kessels, J. Vac. Sci. Technol. A 30, 040802 (2012).

[11] ECS Journal of Solid State Science and Technology – Focus Issue on Atomic Layer Etching and Cleaning.

Leave a Reply